|

情報理論(電気・電子系教科書シリーズ)  情報理論のエッセンス  宇宙を復号する ―量子情報理論が解読する、宇宙という驚くべき暗号 (単行本)  |

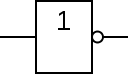

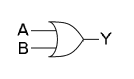

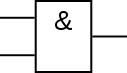

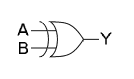

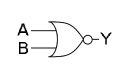

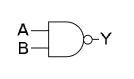

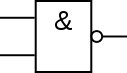

論理回路(ろんりかいろ)は、ブール代数(論理演算)を行う回路。またはデジタル信号を記憶する回路。及びそれらの機能を組み合わせたデジタル回路である。 論理回路の設計論理回路の設計には、論理式や真理値表が用いられる。さらに回路図的な表記手段としてMIL記号など論理素子記号が使われるようになった。 1960年台に登場した標準論理IC(TI社、7400シリーズ)により論理回路の実装が、それまでの個別部品による方法から単純化されアナログ的な回路設計から論理設計が分離できるようになった。 小規模な場合は、論理素子記号などで設計が可能であるが、大規模になると難しい。そのため、1990年代より大規模な回路の設計にはハードウェア記述言語が用いられている。また、集積回路技術の進歩に対応できるように、どのような素子を使用するかに独立なビヘイビアモデル(動作記述)による設計が行われる。 1990年代後半より、試作や少量生産の場合に論理回路をプログラムで書き換え可能なPLDやCPLD、FPGAなどが使用されるようになった。大量生産または高性能が要求される場合はASICも使用される。 完全同期式回路全体で共有するクロック信号を利用して動作のタイミングをあわせる回路である(クロック同期設計)。とくに大規模な回路で広く用いられている。

組み合わせ回路現在の入力のみで出力が決まる回路である。

順序回路過去の内部状態と取得時の入力信号とで出力が決まる回路である。 組み合わせ回路は(内部信号遅延後の)すべての瞬間において、入力の組み合わせだけで出力が一意に決まるが、順序回路は入力信号とともに、内部に保持している過去の状態も出力の決定に関わる。 レジスタ制御信号により現在の入力信号の保持を行うものである。フリップフロップ(FlipFlop)をFFと表記することが多い。 非同期式フリップフロップはクロック入力を持たず、その時点での入力の値(S,R等)に応じて出力が変化し、新たな入力信号が来るまで同じ状態を保持する。

同期式フリップフロップはクロック信号(CLK,CK等と表記)の立ち上がりに同期してその時点での入力の値(D,S,J等)に対応する信号を出力する。この値は次にクロックに立ち上がりが入力されるまで更新されない。

ラッチ(Latch)はG入力の値が1の時に入力されたデータを出力する。G信号が1の間は入力信号の変化に対応して出力も随時変化する。フリップフロップが複数並んだものである。 カウンタ (Counter)ある順序で出力の組み合わせが変化し、一定の周期で元の状態に戻るもので、レジスタとゲートとをいくつか組み合わせたものである。

シーケンサ (Sequencer)外部状況の変化にしたがって定義された演算・動作を行うもので、カウンタ・外部信号のレジスタ・ゲートなどを組み合わせて製作される。 ワイヤード・オア (Wired OR)複数のオープンコレクタ出力を使って便宜上のOR回路を構成する手法。通常は複数のデジタル出力をそのまま結線することは許されないが、オープンコレクタ出力により可能となる。プルアップ抵抗が必要。(7403,7405など) 用途全てのデジタルと名の付く電子機器。コンピュータ、プログラマブルロジックコントローラ(PLC。工業用プロセス制御に用いられる)、CD機器、MD機器、DVD機器、フラットTV、ステレオ、PC、コピー機、プリンタ、デジカメ、ビデオカメラ、家庭用ゲーム機、エアコン、携帯電話、電卓、時計、リモコンなど、今ではほぼすべての電気製品に論理回路が用いられている。他の例としてデジタル信号処理プロセッサなどもそうである。 |